Achievements

差分功耗攻擊(differential power attack, DPA)是一種針對(duì)密碼硬件的側(cè)信道攻擊方式,是當(dāng)今密碼芯片的重要威脅。它通過(guò)分析密碼芯片加/解密過(guò)程中的瞬時(shí)功耗特征獲得參與運(yùn)算的密鑰信息,可以繞開密碼算法的數(shù)學(xué)難題,破解密碼算法。DPA攻擊實(shí)施簡(jiǎn)單,僅需要簡(jiǎn)單的常用裝置和PC機(jī)就可以實(shí)現(xiàn),而且攻擊強(qiáng)度高——未采取防護(hù)措施的普通密碼算法芯片,攻擊者采用DPA攻擊,僅需要幾分鐘就可以獲得密鑰。當(dāng)今日益廣泛應(yīng)用的各類智能卡產(chǎn)品(如門禁卡、付費(fèi)電視卡、USB密鑰、手機(jī)SIM卡等)以及加密U盤、加密硬盤等信息安全設(shè)備無(wú)一例外的都受到DPA的威脅。然而,采取抗功耗攻擊措施,往往帶來(lái)產(chǎn)品成本的增加、功耗的提高和性能的下降,阻礙了上述產(chǎn)品安全性的提高。清華大學(xué)在密碼芯片設(shè)計(jì)技術(shù),特別是抗功耗攻擊技術(shù)方面開展多年研究,已擁有和申請(qǐng)多項(xiàng)專利,所研制的低功耗低成本抗功耗攻擊方法在提供抗DPA能力的同時(shí),能夠有效控制芯片功耗和芯片面積的額外開銷,適用于對(duì)成本敏感、具有低功耗要求的密碼芯片產(chǎn)品。清華大學(xué)采用上述方法設(shè)計(jì)的兩款可抗功耗攻擊的AES加密算法芯片功耗水平和芯片面積均達(dá)到國(guó)際同類芯片的先進(jìn)水平。我們目前面向密碼芯片用戶和設(shè)計(jì)企業(yè),可提供兩款適于不同應(yīng)用要求的AES加密芯片或IP模塊,或根據(jù)用戶需要定制設(shè)計(jì)各類密碼算法芯片和IP模塊。

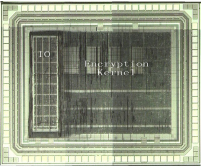

(1)Rijndael算法加密芯片THUDFAES04

功能:支持全部Rijndael加密標(biāo)準(zhǔn),包括明文分組長(zhǎng)度(128位、192位、256位)和密鑰分組長(zhǎng)度(128位、192位、256位)的任意組合;密鑰置入后,如果下一分組不需要更換密鑰則可以只輸入明文分組;輸入模塊采用防惡意干擾設(shè)計(jì)——可以防止攻擊者通過(guò)中斷數(shù)據(jù)輸入過(guò)程篡改密鑰和利用系統(tǒng)內(nèi)部存儲(chǔ)單元的殘存狀態(tài)恢復(fù)有用信息;輸入模塊與輸出模塊彼此時(shí)鐘獨(dú)立,可以在同一時(shí)鐘域也可以在不同時(shí)鐘域。

參數(shù):

l SMIC 0.18 微米2P6M CMOS工藝

l AES-128標(biāo)準(zhǔn)加密一個(gè)分組的能耗為0.053μJ

l 管芯面積: 2.21 mm2(含PAD)

l 吞吐率:AES-128標(biāo)準(zhǔn)下約60Mbps

圖1 Rijndael算法加密芯片THUDFAES04管芯的實(shí)物照片

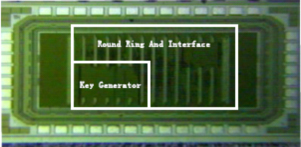

(2)AES加解密芯片THUDFAES06

功能:支持全部FIP-197標(biāo)準(zhǔn)(AES-128/192/256)的加密和解密功能;密鑰置入后,如果下一分組不需要更換密鑰則可以只輸入明文分組;輸入模塊采用防惡意干擾設(shè)計(jì)——可以防止攻擊者通過(guò)中斷數(shù)據(jù)輸入過(guò)程篡改密鑰和利用系統(tǒng)內(nèi)部存儲(chǔ)單元的殘存狀態(tài)恢復(fù)有用信息;輸入模塊與輸出模塊彼此時(shí)鐘獨(dú)立,可以在同一時(shí)鐘域也可以在不同時(shí)鐘域。

參數(shù):

l SMIC 0.18 微米2P6M CMOS工藝

l AES-128標(biāo)準(zhǔn)加密一個(gè)分組的能耗為0.019μJ(不含密鑰擴(kuò)展),一次128位密鑰擴(kuò)展的能耗是0.057μJ

l 面積: 0.43 mm2(含PAD)

l 吞吐率:AES-128標(biāo)準(zhǔn)下約20Mbps

圖2 AES加解密芯片THUDFAES06管芯實(shí)物照片

THUDFAES06相對(duì)于THUDFAES04安全性更高、面積更小,適用于高安全性低吞吐率的應(yīng)用。

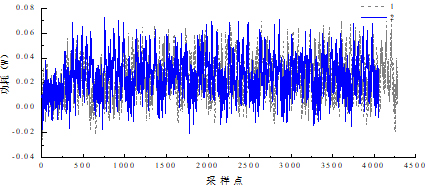

圖3 采用亂序執(zhí)行技術(shù)后實(shí)際測(cè)量得到的功耗軌跡曲線

圖3給出了THUDFAES04芯片執(zhí)行兩次相同的數(shù)據(jù)加密所測(cè)得的功耗曲線,從圖中可以看到,相同的數(shù)據(jù)每次執(zhí)行所產(chǎn)生的功耗軌跡不同,為DPA攻擊制造了困難。

圖4 芯片功能演示和安全性測(cè)試系統(tǒng)照片

上述兩種芯片既可直接作為單獨(dú)的芯片用于設(shè)備中,也可以提供IP核嵌入到SoC芯片中。它們既可以作為協(xié)處理器與其它處理器配合使用,也可以單獨(dú)使用。芯片提供AES算法的核心加解密功能,經(jīng)過(guò)擴(kuò)展或主處理器控制支持各種加密模式。電路采用模塊化設(shè)計(jì),算法執(zhí)行內(nèi)核相對(duì)獨(dú)立,輸入/輸出模塊可根據(jù)應(yīng)用單獨(dú)重新設(shè)計(jì)。電路采用硬件層抗功耗攻擊措施,對(duì)算法無(wú)特殊要求,該技術(shù)可以移植到其它密碼算法的芯片實(shí)現(xiàn)。

移動(dòng)安全設(shè)備、智能卡、RFID等低功耗、低成本要求的信息安全設(shè)備。

采用本算法模塊在幾乎不增加芯片成本的情況下能夠提供高于同類普通產(chǎn)品的安全性和優(yōu)秀的功耗性能,能夠有效增強(qiáng)產(chǎn)品的競(jìng)爭(zhēng)力。上述芯片都已經(jīng)過(guò)實(shí)際加工測(cè)試驗(yàn)證,而且已具有經(jīng)過(guò)驗(yàn)證的實(shí)用芯片和成熟的設(shè)計(jì)方法,無(wú)論直接應(yīng)用還是根據(jù)需要定制設(shè)計(jì)都能夠保證上市時(shí)間的要求,免除了企業(yè)自身的研發(fā)成本和時(shí)間。

(1)芯片供貨;

(2)IP模塊使用授權(quán);

(3)成果轉(zhuǎn)讓;

3應(yīng)用說(shuō)明

4應(yīng)用范圍

5效益分析

6合作方式